# FIDES-P1 AC - DC Power Device

# **AC DIRECT LED DRIVER**

### PRELIMINARY BRIEF DATA

The FIDES free voltage AC to DC LED driver using patented jeong, ym Adaptive AC phase currents to voltages<sup>™</sup> with zero currents valley fill power device is smart LED power driving chipset, It supports all the attractive features of ECO LED lighting products such as high efficiency 95% over with excellent PFC 0.95, ultra small package, low cost, design flexibility, and easy design-in, These parts are targeted to more sophisticated applications and offer several enhanced technology and features, including continuous AC and DC both of input voltage coverage from 10-300 wide ranges and output load up to 5 to 50watts without aluminium electrolytic capacitor and transformer.

The isolation power and non-isolation power for LED switch transistors are external to the main chipset for supports design free are no requires reducing power consumption of the constituent devices such as multi output power provide redundancy.

It also includes built-in features such as a thermal sensor. Direct connection to external ambient sensor is automatic LED brightness control self thermal controller and PLC communication makes smart grid network.

The employed phase current detection technology is automatically current error corrections for each LED load current transition. This phase current driving technology compensate for the regulated AC input with LED loads to independently protection for over power and open or short circuits protection with over-temperature controls.

The chip incorporates a high performance AC to DC in the LED lighting which performs phase slice switch with H bridge advanced CV,CC accurate PWM modulation for constant current by supplied voltaic driving it ideal for configuration to multiple LED applications.

These features simplify the task of the LED monitor back light or LED bulb. QFN36 small package supports the smart fixture design and allows for the use of lower-end factories.

# **FEATURES**

- Free input AC10~300V range

- Un regulated DC input

- Un to 3 LFD aroun in series

- E FIDES-P1 QFN-36 to extend LED life time, day and night luminance power configurable

- Direct connect illumination driver

Installed

- 125°C shutdown and selectable temperature (60°~125°) synchronized controller embedded

- On/Off and dimming by PLC modem to seamless attachable option (SPI)

- -40°C +85°C

#### TYPICAL APPLICATIONS

- LED TV, Monitor, High power LED lighting

- Etc

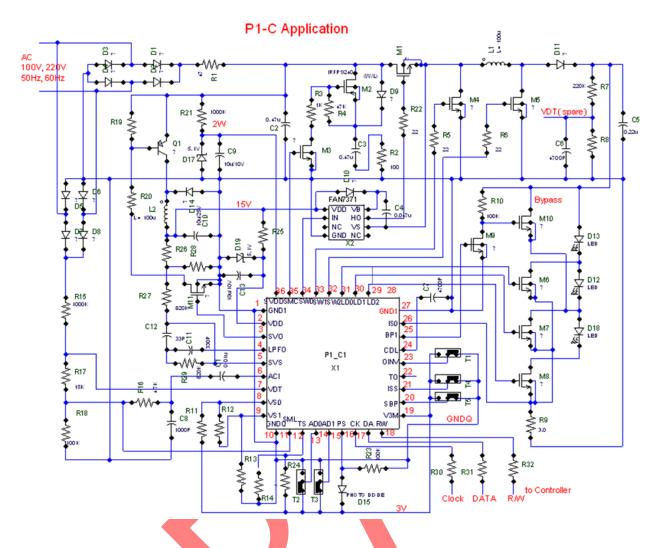

# **Typical Application Circuit**

# Terminal descriptions

IO: I=input, O=output, B=Bidirectional, -= no connection

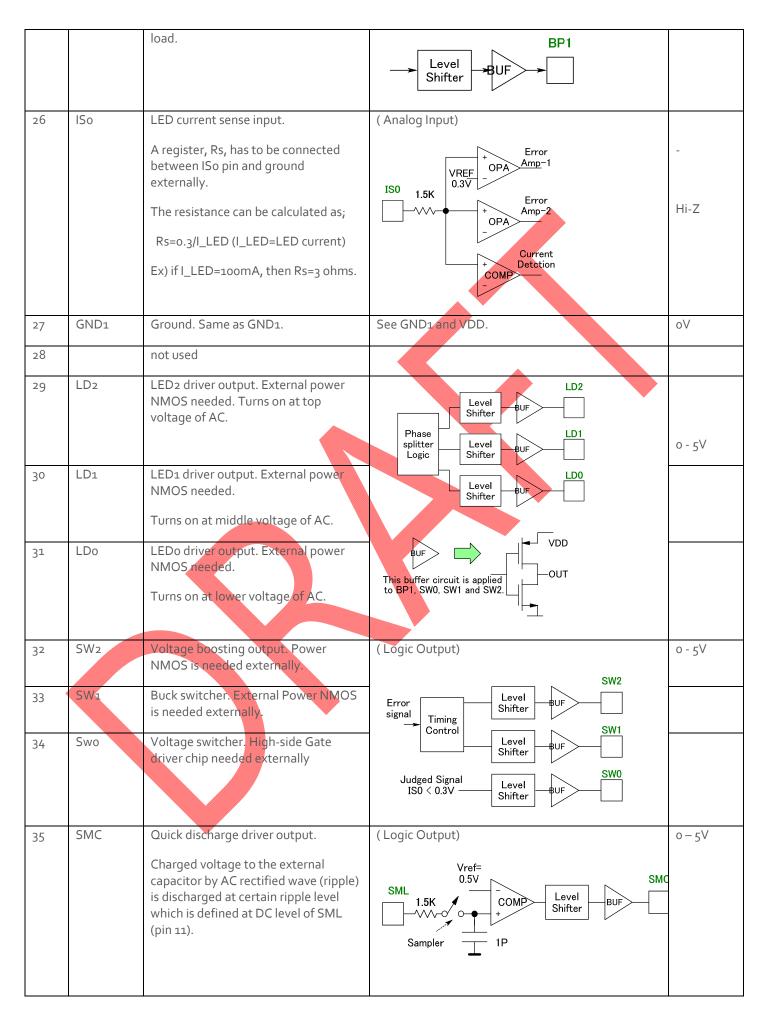

| Pin | Pin     | Description                                                                                                                                    | Circuit                        | Voltage |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------|

| #   | Name    |                                                                                                                                                | ( shows Input or Output port ) |         |

|     | General | Every pins except ground and power supply pins have ESD (Electrical Static Damage) protection diodes between pin and ground and VDD potential. | Pin GND1                       |         |

| 1   | GND1    | Ground for large current. Connect to near minus port of bridge rectifier diode.                                                                | ( Bi-directional)              | 5V      |

| 2  | VDD  | Power supply for chip                                                | VDD                               |        |  |

|----|------|----------------------------------------------------------------------|-----------------------------------|--------|--|

|    |      | 5 +/- 0.5V                                                           |                                   | 0V     |  |

|    |      |                                                                      |                                   |        |  |

|    |      |                                                                      | GND1                              |        |  |

|    |      |                                                                      |                                   |        |  |

| 3  | SVO  | PWM output for sub-regulator                                         | (Logic Output)                    | 0 – 5V |  |

|    |      | The NMOS load is needed.                                             | VDD                               |        |  |

|    |      |                                                                      | svo                               |        |  |

|    |      |                                                                      |                                   |        |  |

|    |      |                                                                      | GNDT                              |        |  |

| 4  | LPFO | Low pass filter output for sub-regulato                              |                                   | 0.3 -  |  |

| 4  | LPFO |                                                                      | (Arialog Gutpat), (Arialog liput) | 4.5V   |  |

|    |      | Load impedance: >100Kohm                                             | LPF0                              |        |  |

| 5  | SVS  | Low pass filter input for sub-regulator.                             | SVS 1.5K 1.5K                     | 1.16V  |  |

|    |      | Lag-lead LPF can be available to connect capacitors and resistors    | OPA +                             |        |  |

|    |      | externally between SVS and LPFO.                                     | COMP                              |        |  |

|    | ACI  | Full wave AC signal input. Vin= 1 to                                 | (Analog Input)                    | 1.66V  |  |

| 6  | ACI  | 2Vpp.                                                                |                                   | 1.00 V |  |

|    |      | Attention has to be paid to the PC                                   | AGI 150K                          |        |  |

|    |      | pattern layout in order to avoid noise injection through PC pattern. | 5P COMP                           |        |  |

|    |      | injection unought o pattern.                                         |                                   |        |  |

| 7  | VDT  | AC signal input for multi-phase generation.                          | (Analog Input)                    |        |  |

|    |      |                                                                      | VDT 1.5K                          | -      |  |

|    |      | This pin is valid while ISS pin is set to zero level.                |                                   | (Hi-Z) |  |

|    |      | ( The AC signal has to be detected                                   | ISO                               |        |  |

|    |      | before the rectifier)                                                |                                   |        |  |

| •  |      |                                                                      | ISS                               |        |  |

| 0  | 1/00 | Potoronoo voltogas for AC shees as                                   | lo (Angleg Input)                 |        |  |

| 8  | VS0  | Reference voltages for AC phase ang generation.                      |                                   |        |  |

| 9  | VS1  | VS0: high side of reference voltage                                  | VDT  1.5K  Select                 | -      |  |

|    |      | VS1: low side of reference voltage                                   | ISO Select or COMP                |        |  |

|    |      |                                                                      | to Encoder                        | Hi-Z   |  |

|    |      |                                                                      |                                   |        |  |

|    |      |                                                                      | VS1 2K COMP                       |        |  |

| 10 | GNDQ | Quiet ground for mainly analog circuit.                              |                                   | 0      |  |

|    |      | The potential of this ground should be higher than GND1.             |                                   |        |  |

|    | CNAL |                                                                      |                                   |        |  |

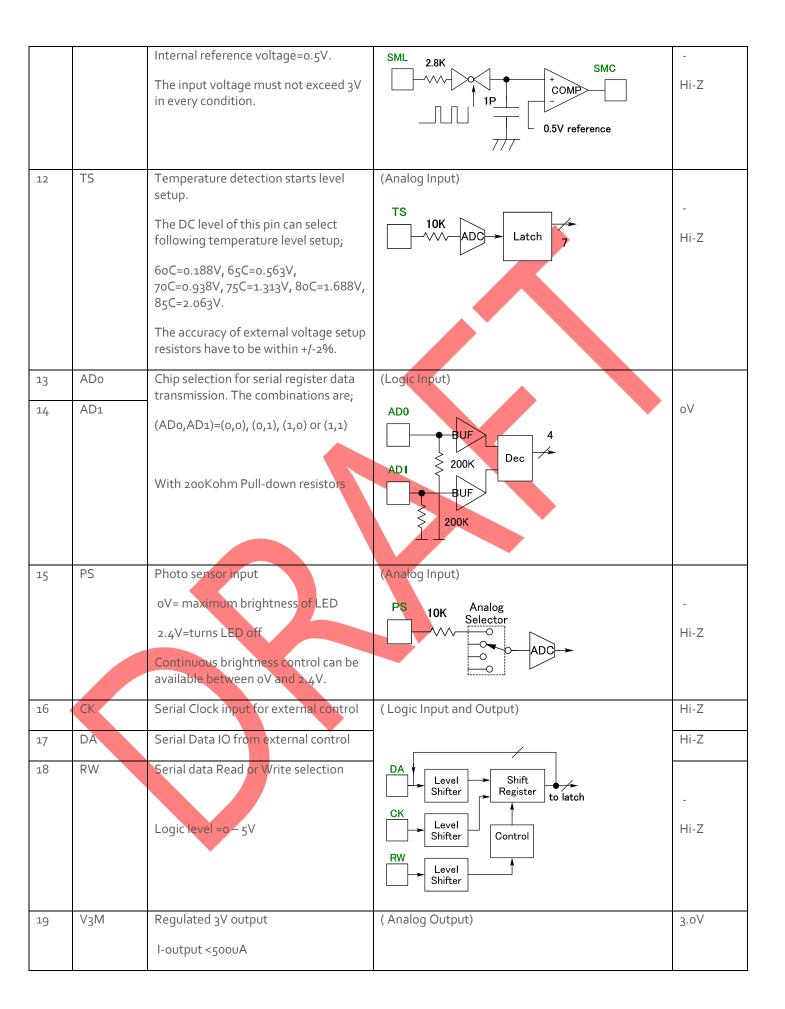

| 11 | SML  | Voltage setup for quick charge level. (Analog Input)                 |                                   |        |  |

| 36 | SVDD | Sub-regulator power supply | SVDD | 5.0V |

|----|------|----------------------------|------|------|

|    |      | SVDD=5.0+/-0.5V            |      |      |

|    |      |                            | GND1 |      |

|    |      |                            |      |      |

| Item                    | Symbol | Parameter                              | min     | typ | max     | unit       | Condition          |

|-------------------------|--------|----------------------------------------|---------|-----|---------|------------|--------------------|

| Rated Voltage<br>Range  | VDD    |                                        | 4.5     | 5.0 | 5.5     | V          | Max V =6.0V        |

| Junction<br>Temperature | Tj     |                                        | -40     | 25  | 125     | $^{\circ}$ |                    |

|                         |        |                                        |         |     |         |            |                    |

| Logic Low input V       | ViL    | ADO, AD1,ISS, SBP, RW, CK, DA, REGSEL, | 0       |     | 0.2VREF | V          |                    |

| Logic High input V      | ViH    | OINV                                   | 0.8VREF |     | VREF    | V          |                    |

| Logic Low output V      | VoL    |                                        | 0       |     | 0.2VREF | V          |                    |

| Logic High output V     | VoH    | DA Tamainal                            | 0.8VREF |     | VREF    | V          |                    |

| Low Level output I      | IoL    | DA Terminal                            |         |     | -1      | mA         |                    |

| High Level output I     | ІоН    |                                        | 1       |     |         | mA         |                    |

| Switch Clock Freq       | FCLK   |                                        |         | 200 |         | KHz        |                    |

| Dimmer range            | DIM    |                                        | 1       |     | 255     |            |                    |

| Drive current           | I_DRV  | LD0-2、SW0,1,2,3 Terminal               | 40      |     |         | mA         |                    |

| Regulator output        | VREF   | VREFO Terminal                         | 2.95    | 3.0 | 3.05    | V          |                    |

| Max AC V detect         | V_AC   | VDT Terminal                           | 0       |     | VDD     | V          |                    |

| LEDV divide             | V_LEDD | VS0, VS1                               | 0.1     |     | VDD     | V          |                    |

| Ambient detect          | VL     | PS Terminal                            | 0.15    |     | 1.5     | V          |                    |

| LEDcurrent<br>Threshold | VTHIS  | ISO Terminal                           |         |     |         | V          | Comparate with saw |

|                         |        |                                        |         |     |         |            |                    |

| Power consumption       |        |                                        |         |     | 5       | mA         |                    |

Table 1

Monitored signal selection (Output at "TO")

| # | MON   | T0 S<3>=0                       | Voltage | T0 S<3>=1                   | Volt |

|---|-------|---------------------------------|---------|-----------------------------|------|

|   | <3:0> |                                 |         |                             | -age |

| 0 | 0000  | 0pen                            | -       | 0pen                        | -    |

| 1 | 0001  | GNDQ ( quiet Ground)            | 0       | GNDQ ( quiet Ground)        | 0    |

| 2 | 0010  | BGRO(Band Gap Regulator) output | 1. 16V  | RNX( Power On reset output) | 0    |

| 3   | 0011 | V3Q (Quiet 3V)                      | 3V     | V3N (Noisy 3V)                               | 3V    |

|-----|------|-------------------------------------|--------|----------------------------------------------|-------|

| 4   | 0100 | VHA (ADC6 Reference High Voltage)   | 2. 43V | VLA(ADC6 Reference Low Voltage)              | 1. 7V |

| 5   | 0101 | ADTA (Temperature voltage for ADC)  | 3V     | TAO (Temperature Sense Voltage)              | 1.85V |

| 6   | 0110 | GNDQ (quiet Ground)                 | 0      | GNDQ (quiet Ground)                          | 0     |

| 7   | 0111 | VSWO (Saw Tooth wave of main reg)   | 2V     | ISO00 ( LED Current Sense<br>Buffer Voltage) | 0. 3V |

| 8   | 1000 | CK39 (Around 39Hz output)           | Pulse  | ILMLO (ISO00 & 0.12V Comparator Output)      | 0     |

| 9   | 1001 | CK78 (Twice Frequency of CK39)      | Pulse  | CK10K (10KHz clock output)                   | Pulse |

| 1 0 | 1010 | CKMON (Clock Signal)                | Pulse  | DMO ( Dimmer Pulse output)                   | Pulse |

| 1 1 | 1011 | ISRPO (Error Amp Comparator Output) | 0      | LSRPO ( Error Amp ILM Output)                | Pulse |

| 1 2 | 1100 | ACZ (AC zero Cross Output)          | Pulse  | ACPLS -Not used                              |       |

| 1 3 | 1101 | MODU (DUEN (Up/Down) Output)        | Pulse  | MOMCK (Sub -reg clock output)                | Pulse |

| 1 4 | 1110 | SHTDWN (Shut Down at Tj>125C)       | 0      | 0pen                                         |       |

| 1 5 | 1111 | 0pen                                |        | Open                                         |       |

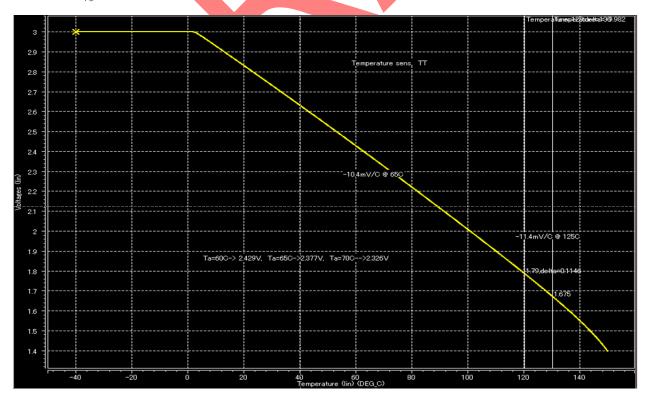

Internal temperature sensor temp vs V

Shutdown V = 1.79V

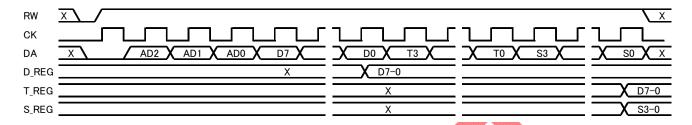

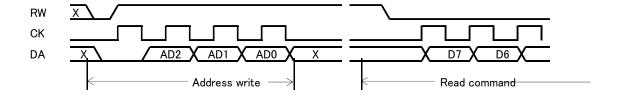

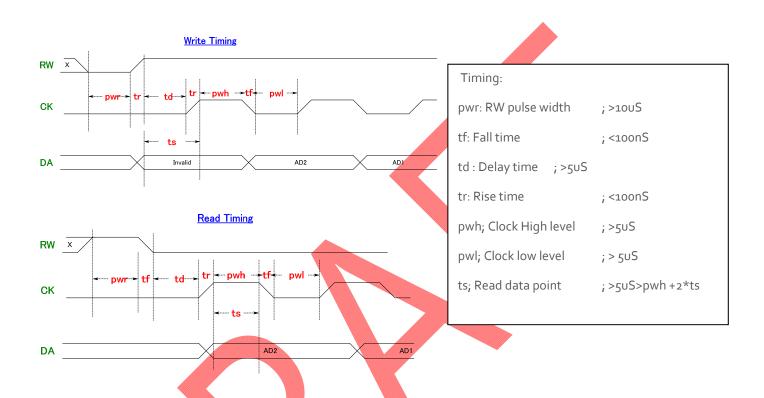

## SPI interface timing

Host MPU to P1 data write.

P1 send the data to host MPU.

#### Write timing

D7-0 : Dimming data(Write)

AD2\_0: Chip address data(0-7)

D\_REG : dimming data(resistor output)

T\_REG: test data(registor output); Select the test monitor output

S\_REG : test data(register output) ;

$S<1>=0 \rightarrow PS$  data enable  $S<1>=1 \rightarrow Dimmer$  data change by register

$S<3>=0 \rightarrow Test output$   $S<3>=1 \rightarrow Test 2 output$

P1 will be edge detection from CK and ignored first data.

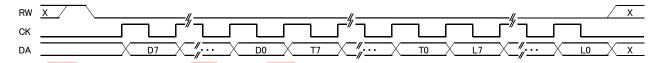

# Read timing

D7-0: Dimming data(Read)

T7-0: Temperature data

L7-0: Photo diode ambient data

P1 can read edge rise of CK and MPU can edge down of CK read.

# **Detailed Description**

The FIDES-P1 is a highly integrated, flexible, multi-string LED driver that uses external MOSFETs to allow high LED string currents and, includes temperature power supply control to maximize LED life efficiency. The driver optionally connects to a LED string faults fix-up functions help to black out of luminaire system.

The easy install to plug in light sensor offers automatic dimming control for intelligent ECO power saving. Synchronization for use in FIDES SPI format to controlled LED TV backlight applications.

The drivers provide multiple methods of controlling LED brightness, through both peak current control and pulse width control of the PLC and light sensor, internal temperature drive signals. Peak temperature control offers excellent MTBF consistency, while pulse width control allows brightness management.

An on-chip temperature sensor allows to select variable register values. When reaching over temperature it, automatically shut-downs or decrees power driving. All resister values can be modified through the serial interface if a different power condition is desired.

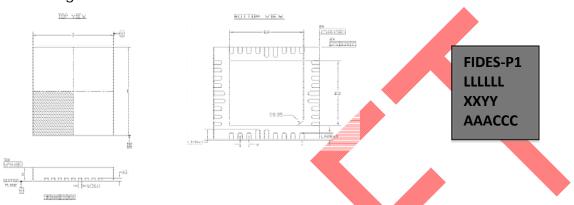

# QFN-36 Package Typical Pad Layout

# QFN-36 Package Dimension

| S      | COMMON                |      |      |                 |           |       |  |

|--------|-----------------------|------|------|-----------------|-----------|-------|--|

| SYMBOL | DIMENSIONS MILLIMETER |      |      | DIMENSIONS INCH |           |       |  |

|        | MIN,                  | NDM. | MAX. | MIN.            | NDM.      | MAX.  |  |

| Α      | 0.85                  | 0.90 | 0.95 | 0.034           | 0.036     | 0.038 |  |

| АЗ     | 0.203 REF             |      |      | 0               | ,008 REF  | -     |  |

| b      | 0.20                  | 0.25 | 0.30 | 0.008           | 0.010     | 0.012 |  |

| D      | 5.85                  | 6.00 | 6.15 | 0.230           | 0.236     | 0.242 |  |

| DS     | 4.10                  | 4.20 | 4,30 | 0.161           | 0,165     | 0.170 |  |

| E      | 5.85                  | 6.00 | 6.15 | 0.230           | 0.236     | 0.242 |  |

| E2     | 4.10                  | 4.20 | 4,30 | 0,161           | 0.165     | 0.170 |  |

| e      | 0.500 BSC             |      |      | C               | 0.050 B20 |       |  |

| L      | 0.40                  | 0,45 | 0.50 | 0.016           | 0,018     | 0,020 |  |

| L1     | 0.60                  | 0.65 | 0.70 | 0.024           | 0.026     | 0,028 |  |

The FIDES-P1 is supplied in a RoHS compliant leadless QFN-36 package. The package is lead (Pb) free, and uses a 'Green' compound. The package is fully compliant with European Union directive 2002/95/EC.

This package is 6mm x 6mm. The solder pads are on a 0.50mm pitch. The above mechanical drawing shows the QFN-36 package. All dimensions are in millimeters.

The center pad on the base of the FIDES-P1 is internally connected to AGND.

The date code format is XXYY where XX = two-digit week number, YY = two-digit year number.

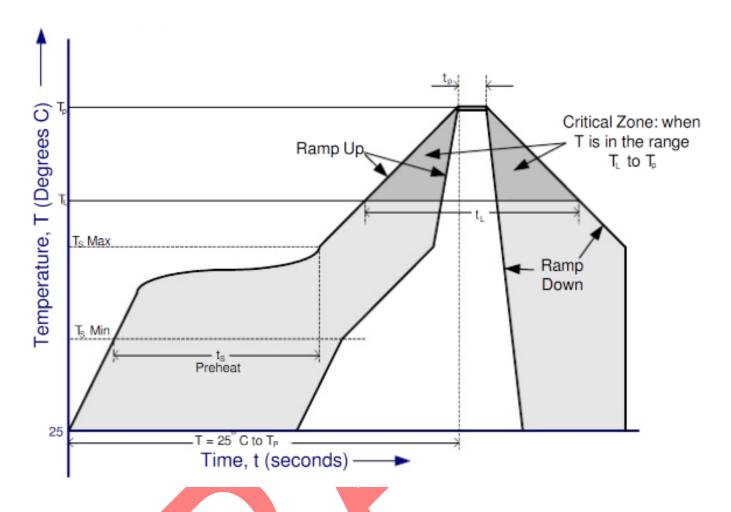

# **Solder Reflow Profile**

The FIDES-P1 is supplied in Pb free QFN-36 package.

The recommended solder reflow profile for package options is show above.

#### **Table for Reflow Profile Parameter Values**

The recommended values for the solder reflow profile are detailed in this table. Values are shown for both a complete Pb free solder process.

| Profile Feature                                                                                                                           | Pb Free Solder Process              | Non-Pb Free Solder Process          |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------|

| Average Ramp Up Rate (Ts to Tp)                                                                                                           | 3°C / second Max.                   | 3°C / Second Max.                   |

| Preheat - Temperature Min (T <sub>s</sub> Min.) - Temperature Max (T <sub>s</sub> Max.) - Time (t <sub>s</sub> Min to t <sub>s</sub> Max) | 150°C<br>200°C<br>60 to 120 seconds | 100°C<br>150°C<br>60 to 120 seconds |

| Time Maintained Above Critical Temperature $T_L$ : - Temperature $(T_L)$ - Time $(t_L)$                                                   | 217°C<br>60 to 150 seconds          | 183°C<br>60 to 150 seconds          |

| Peak Temperature (T <sub>p</sub> )                                                                                                        | 260°C                               | 240°C                               |

| Time within 5°C of actual Peak Temperature $(t_p)$                                                                                        | 20 to 40 seconds                    | 20 to 40 seconds                    |

| Ramp Down Rate                                                                                                                            | 6°C / second Max.                   | 6°C / second Max.                   |

| Time for T= 25°C to Peak Temperature, $T_p$                                                                                               | 8 minutes Max.                      | 6 minutes Max.                      |

## © 2012 FIDES. All rights reserved. / Rev.: FIDES P1 DEC 2012

FIDES, logo and combinations thereof, and others are registered trademarks or trademarks of FIDES Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with FIDES products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of JEONG YEONMOON.

EXCEPT AS SET FORTH IN THE FIDES TERMS AND CONDITIONS OF SALES LOCATED ON THE FIDES WEBSITE, FIDES ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY

RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT.

IN NO EVENT SHALL FIDES BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF LGC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

FIDES makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. FIDES does not make any commitment to update the information contained herein. Unless specifically provided otherwise, FIDES products are not suitable for, and shall not be used in, automotive applications. FIDES products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.